# ATARI Computer GmbH Technologiezentrum

The second secon

# AMI-386 BIOS PLUS USER MANUAL

American Megatrends Inc. 4025 Pleasantdale Road, Ste 320 Atlanta, Ga - 30340

Ph. (404) 263 8181 Fax. (404) 263 9381

1

# Table Of Contents

# Section 1

| Installing the AMI-386 BIOS                  | . 3  |  |  |  |  |  |  |

|----------------------------------------------|------|--|--|--|--|--|--|

| Memory Test Bypass                           | . 3  |  |  |  |  |  |  |

| CMOS Setup                                   | . 4  |  |  |  |  |  |  |

| Summary of Set-up                            | . 6  |  |  |  |  |  |  |

| When does the BIOS prompt you to run Set-up? | . 7  |  |  |  |  |  |  |

| Errors Reported By AMI-BIOS                  | . 8  |  |  |  |  |  |  |

| Appendix B & Figures                         | . 23 |  |  |  |  |  |  |

| Section 2                                    |      |  |  |  |  |  |  |

| Overview                                     | . 10 |  |  |  |  |  |  |

| Hard Disk Diagnostics                        | . 12 |  |  |  |  |  |  |

| Floppy Diagnostics                           | . 16 |  |  |  |  |  |  |

| Keyboard Diagnostics                         | . 18 |  |  |  |  |  |  |

| Video Diagnostics                            | . 19 |  |  |  |  |  |  |

| Miscellaneous Diagnostics                    | . 20 |  |  |  |  |  |  |

| Appendix A                                   | . 21 |  |  |  |  |  |  |

#### Section 1

#### 1.0 BIOS Overview

This guide explains how to:

- a) Install the AMI-386 BIOS.

- b) Use the built-in Set-up Procedure.

- -c) Select the Clock Speed / Wait States through the Keyboard.

- d) Interpret the errors reported by the AMI-BIOS.

- e) Use the 3 1/2" floppy drive support effectively.

#### 2.0 Installing the AMI-386 BIOS

Skip this paragraph if the BIOS is already plugged on the MotherBoard.

Before you begin the installation ensure the following:

- i ) The Board is powered down.

- ii) ROM's are susceptible to static electricity. So observe the following precautions when you handle a ROM:

- a) Unpack the ROM's on a ground connected anti-static mat.

- b) Wear an anti-static wristband, grounded at the same point as the anti-static mat.

(A cheaper solution is to use a sheet of conductive aluminium foil grouded through a 1 Mega-ohm resistor instead of an anti-static mat. Similarly, a strip of conductive aluminium foil wrapped around the wrist and grounded through a 1 Megaohm resistor will serve the purpose of a wrist band.)

Ensure that the ODD & EVEN BIOS go into their respective sockets.

#### 3.0 Starting Up The System

Power up the system and wait for the BIOS to show up the BIOS activity on the screen.

#### 4.0 Memory Test Bypass

The BIOS performs diagnostics of the system and displays the size of the memory being tested.

Note that you can bypass the memory test by pressing the <ESC> key. This option would be quite useful when the memory on the system is quite large. You should hit the <ESC> key when the message Press <ESC> Key to bypass MEMORY test appears on the screen.

Also note the Ref. number at the bottom of the screen. Make a note of this number before you call Customer Support at AMI for assistance with the BIOS.

#### 5.0 CMOS Setup

Immediately after the memory and cache test, you will get the following prompt on the screen:

Press <DEL> key to run SETUP Utility

Hit <DEL> key to get into the Setup Mode. Note that <DEL> key will get you into the set-up mode only when the message:

Press <DEL> key to run SETUP Utility, is displayed on the screen.

If you hit <DEL> key the following message appears on the screen: WANT TO RUN SETUP UTILITY (Y/N)?

If you hit <Y> or <y> and the <ENTER> key you have the Setup screen.

5.0.1 Time/Date Setup

The Setup screen looks like below:

CMOS SETUP

Curret date is: XX-XX-XXXX

Enter new date (MM-DD-YYYY)?

To this question you would have to enter the date in the format shown on the screen.

If you feel that the current date should remain unchanged, you would just have to hit the <ENTER> key. In such a case the new date is set to the same value as the current date.

The next question you have on the screen is:

Current time is :XX:XX:XX Enter new time (HH:MM:SS)?

To this question you key in the time in the format defined. Press <ENTER> key alone if the current time is right.

As soon as you have done this the BIOS shows you the type of the display on your system.

After that, the setup takes two differet paths depending upon the CMOS being initialized or uninitialized.

#### 5.0.2 CMOS Initialized

Under these conditions you would see the following messages:

Fixed disk drive C type : X (if installed else Not Installed.)

- Fixed disk drive D type : X (if installed else Not Installed.)

Diskette drive A is 3 1/2"

Diskette drive B is: Double Sided (Other options as above)

Base Memory Size is: XXX KB

Expansion memory size is: XXXX KB

Are these options correct (Y/N)?

Note that the information about Drive A indicates 3 1/2", as CMOS had been set earlier to reflect this status. If on the contrary, CMOS had been set for a 1.2 MB drive, the message in place of 3-1/2" it would be High Capacity.

If you feel that the information displayed above is right, hit <Y> and the <ENTER> key to proceed to system boot with the new information.

#### 5.0.3 CMOS Uninitialised

#### 5.0.3.1 Disk Drive Type Definition

In this case you would have to enter the type of the fixed Drive C in response to the message:

#### \*\*\*\* WARNING \*\*\*\*

Entering the wrong disk drive TYPE causes improper operation of the disk. If disk not installed press <RETURN> For disk TYPE details press <ESC>

Enter disk drive C type (1-47)?

Note that the disk type details are only a key stroke away. Hit <ESC> key to find for yourself. You could always come back by hitting <ESC> again. Refer to Appendix B for drive details.

Once you have convinced yourself about the drive type enter the appropriate number and hit <ENTER>.

Note that pressing <ENTER> key alone indicates the absence of the Drive

You would then be asked to enter the type of the disk Drive D. The procedure for doing this is the same as that for Drive C. Remember if you do

not have disk Drive D on your system, you just have to hit the <ENTER> key.

6.0 Floppy Drive Type Definition

Diskette drive A is 3 1/2" (Y/N)?

- -The above question is asked if the drive has been found to have 80 tracks. Since a drive with 80 tracks could either be a

- high capacity i.e 1.2 MB drive

- or 3 1/2" i.e 720 KB drive,

you would have to answer this question.

By entering <N> or <n> you can select the high capacity drive. Alternatively enter <Y> or <y> to select a 720 KB drive. This question could come up for the case of drive B as well provided it has been detected as a 80 track drive by the BIOS.

If you hit the <ENTER> key alone, the BIOS assumes the drive to be a 1.2 MB drive.

At this point you have entered all the information the BIOS requires for starting up the system.

BIOS detects a few details by itself, e.g. the diskette drive type in case of a 360 KB drive as shown below:

Diskette drive B is : Double Sided (Other options as above)

Base Memory Size is : XXX KB Expansion memory size is : XXXX KB

Are these options correct (Y/N)?

If you are convinced at this stage that all the information you have entered upto this point is right, hit <Y> or <y> key followed by <ENTER> key. When you do this the BIOS goes all over again to boot up the system with the information specified.

However, if you would like to modify some information, then you should hit either <N> or <n> key followed by enter. You would now go through the setup all over again.

#### 7.0 Summary of Set-up

The Set-up screen thus requires you to set

- a) Date.

- b) Time.

- c) Hard Disk Type For Drive C (if present).

- d) Hard Disk Type For Drive D (if present).

- The Set-up procedure also automatically detects the following:

- a) Type Of Display Card.

- b) Size Of Real Memory.

- c) Size of Memory beyond 1 MB.

- d) Presence of 360 kb floppy drives.

- e) Presence of a 80287.

Also, if a second Hard Disk drive is physically connected but the CMOS is not set for this Drive D, the BIOS informs you about the same and gives - you a chance to configure the drive through SETUP.

- Having setup the CMOS, the BIOS runs through the diagnostics again, tests the memory, sets up the devices configured and proceeds to boot.

Note that the Set-up option is available even after a soft reset.

8.0 When does the BIOS prompt you to run Set-up?

The BIOS prompts you to run Set-up under the following conditions

- a) CMOS options not set.

- b) Display Configuration Mismatch.

- c) Memory Size mismatch.

- d) Hard Disk Set-up error.

- e) CMOS battery is low.

- f) An additional hard disk presence is detected.

# 9.0 Selecting Clock Speed/Wait States

AMI-BIOS allows you to change Clock Speeds and Wait States through the keyboard at any time. Following are the key combinations and their meanings:-

Kev Combinations

1. <CNTRL><ALT><+>

Meaning Switch to high speed.

2. <CNTRL><ALT><->

Switch to low speed.

- 3. <CNTRL><L.SHIFT><ALT><+> Switch to zero Wait state.

- 4. <CNTRL><L.SHIFT><ALT><-> Switch to one Wait state.

### 10.0 Errors Reported By AMI-BIOS

AMI-BIOS performs various diagnostic tests at the time the system is powered up. Whenever an error is encountered during these tests, either you hear a few short beeps or see an error display on your monitor. If the error occurs before the display device is initialised the system reports the error by giving a number of short beeps.

If the error is FATAL then system halts after reporting the FATAL error. If the error is NON-FATAL the process continues after reporting the NON-FATAL error.

#### 10.0.1 Fatal Errors

| -    |        |                                       |

|------|--------|---------------------------------------|

| Ве   | ep Cou | nt Meaning                            |

| # to | 1      | DRAM refresh failure.                 |

| -    | 2      | Parity Circuit failure.               |

|      | 3      | Base 64KB RAM failure.                |

|      | 4      | System Timer failure.                 |

|      | 5      | Processor Failure.                    |

|      | 6      | Keyboard Controller - Gate A20 error. |

|      | 7      | Virtual Mode Exception Error.         |

|      | 8      | Display Memory R/W Test Failure. (*)  |

|      | 9      | ROM-BIOS CheckSum Failure.            |

#### (\*) Non-Fatal Error.

### 10.0.2 Error Messages

#### Fatal Errors

- 1. Channel 2 of Timer Not functional.

- 2. Stray Interrupt sensed in controller.

- 3. Interrupt controller #2 not functional.

#### Non-Fatal Errors

- 1. Keyboard Error.

- 2. Keyboard/Interface Error.

- 3. CMOS battery state low.

- 4. CMOS system options not set.

- 5. CMOS checksum failure.

- 6. CMOS memory size mismatch.

- 7. CMOS system time and date not set.

- 8. CMOS display configuration mismatch.

- 9. Display setting not proper.

- 10. Keyboard is locked ..... Unlock it.

- 11. Floppy disk controller failure.

- 12. Hard disk unit 0 error.

- 13. Hard disk unit 1 error.

- 14. Hard disk unit 0 failure.

- 15. Hard disk unit I failure.

- 16. Hard disk unit 1 is not defined in CMOS.

- 17. Cache Memory Bad Do Not Enable Cache.

# 11.0 Use of 3 1/2" Support Effectively

DOS 3.20 provides support for 3 1/2" drives. For this purpose it needs support from the ROM BIOS. AMI-BIOS release date 12/03/86 onwards provides the necessary support.

The 3 1/2" drive can be freely configured as Drive A or Drive B with this

BIOS. Thus it is possible to boot off directly from a 3 1/2" drive.

Earlier versions of DOS would require the use of DRIVER.SYS to provide the necessary support.

A few points would have to be kept in mind when you use the 3 1/2" drive and a 1.2 MB together. Ensure that when you perform the Setup you define the drives correctly. Incorrect definition could make the drive unusable.

The table below describes the valid combinations on a AT:

| CMOS Status | Physical | Drive Status | Functional |

|-------------|----------|--------------|------------|

|             |          |              |            |

| 1.2 MB      | 1.2 MB   | YES          |            |

| 3 1/2"      | 3 1/2"   | YES          |            |

| Undefined 1 | .2 MB    | YES          |            |

|             |          |              |            |

The remaining combinations are invalid. Please make a note of these combinations before you call us for help.

Should you feel that you need assistance with the BIOS at any stage, call AMI Tech. Support at (404) 263-8181.

#### Section - 2

#### 1.0 Overview

AMI-386 BIOS PLUS provides the following in a ROM:

a) Field proven extensively used AMI-386 BIOS.

b) Built-in CMOS setup utility with support for 47 Disk drive types, 3 1/2" Floppy Disk drives & Enhanced Keyboard.

c) A Diagnostics program - superior to the IBM Advanced Diagnostics - with special enhancements & a user-friendly interface.

d) A Built-in Calendar.

This portion of the manual explains how to use the Diagnostics program alone.

386 BIOS PLUS comes in 256K ROM chips. Hence make sure that when vou plug these ROMs that the DIP Switch on the System Board is set to indicate 256K Chips.

#### 2.0 Selecting The Diagnostics Option

Hit the <DEL> key on the numeric keypad when you see the following message at the time of system startup:

#### Press <DEL> Key to run SETUP or DIAG

The above message is seen on the 4th line of the screen.

Hitting <DEL> key brings the following message after a few seconds on the screen:

### Want to run SETUP or DIAG (Y/N)?

If you answer <Y> or <y> followed by <ENTER> then you would be asked to select either Setup or Diagnostics as shown below:

### SETUP or DIAG (1/2)?

Hit <1> to use the built-in SETUP option.

Hit <2> to use the Advanced Diagnostics option.

#### 3.0 Diagnostics Menu

Note the following in the Diagnostics Opening Menu:

- a) The <u>Guide Line</u> in Reverse Video specifying the usage of the Cursor Keys, <ENTER> & <ESC> key.

- b) The Configuration of the system in the "Devices Present" box.

- c) The Real Time Clock ticking away at the right hand top corner of the screen.

- d) Diagnostics Options Line Hard Disk, Floppy, Keyboard, Video & Miscellaneous Diagnostics.

- e) Hard Disk <u>Diagnostics Options Window</u> detailing the various hard disk diagnostics that are available.

- f) Note that the Block Cursor is on the <u>Hard Disk</u> & the first option under hard disk diagnostics <u>Hard Disk Format</u>.

#### 4.0 Key Conventions

Use the Left & Right arrow keys to move in the Diagnostics Options Line.

Use the Up & Down arrow keys to move within a Diagnostics Options Window.

Use the <ENTER> key to select the option in the Diagnostics Options Window.

Use <ESC> key to abort & return to previous menu.

### 5.0 Diagnostics Options Window

The individual diagnostics options are as below:

- 1. Hard Disk options.

- 2. Floppy Disk drive options.

- 3. Keyboard options.

- 4. Video options.

- 5. Miscellaneous options.

#### Hard Disk Diagnostics

# 1.0 Using Hard Disk Options

The Hard Disk options discussed below fall in two categories:

a) Destructive Operation - The data on the Hard Disk is lost.

b) Non-destructive Operation - The data on the Hard Disk is undisturbed.

The list below gives the various Hard Disk Options & the category they fall in:

a) Hard Disk Format

b) Auto Interleave

c) Media Analysis

d) Performance Test

e) Seek Test

f) Read/Verify Test

Destructive Operation.

c) Destructive Operation.

c) Non-destructive Operation.

c) Non-destructive Operation.

g) Check Test Cylinder - Data on the Test Cylinder alone is lost.

All the options under Hard Disk Diagnostics require more or less the following inputs:

- a) Disk Drive

- b) Drive Type

- c) Interleave Factor

- d) Bad Track List

- e) Start Cylinder

- f) End Cylinder

- g) Start Head

- h) End Head

All the above input fields have a default value. Thus a user need not necessarily key-in all the inputs.

We shall discuss the inputs required & their meaning for Hard Disk Format Option. This discussion can however be extended for the rest of the Hard Disk Options.

# 2.0 Hard Disk Format Option - (Destructive Operation)

Figs 6 & 7 reflect the various screens the user goes thru' when this option is selected.

Note that in case of a single drive System the disk drive for the operation is assumed to be drive C.

#### a) Drive Type Definition

The default value for the drive type is the SETUP value set during the CMOS setup.

However if the drive was not set during CMOS Setup, the user now has an option of setting the drive to be one among the 46 standard Disk drive types.

Note that all the information about the drive unfolds when the disk drive type is being chosen.

If the disk drive type does not fall within the 46 standard disk types, use the USER option to define your own parameters for the drive.

Note that this USER definition is valid only as long as the Diagnostics is in effect. This feature is provided for you to test a disk drive, the definition for which is not available in the ROM.

#### b) Interleave Factor

Choose an optimum interleave factor. Refer to the Appendix - A for details on how to decide on an Optimum interleave.

The default value for the interleave factor is 3.

#### c) Mark Bad Tracks

If the manufacturer has defined certain bad patches on the disk, enter <Y> to this question.

The user then goes into a menu which allows for complete editing of the bad track list.

Exit Bad track entry by hitting <ESC> or selecting the <u>Save And Exit</u> option. Note the usage of <ESC> key here.

The default answer for this question is <N>.

#### d) Cylinder Number

Enter the Start & End Cylinder Number if you want to override the defau-

The same is true for Start & End Head number.

The default value for the start Cylinder & Head is 0 and that of the End cylinder & head is the value of the maximum cylinder & head respectively.

#### e) Proceed

If all the entries are correct, you could hit <Y>. Else you could say <N> & go over all the entries again. The default answer is <N>.

#### f) Warning

If you had hit <Y> to the previous question, you get a WARNING message. You could proceed to format if you are absoulutely sure about the information you have entered upto this point.

### g) Activity Screen

PLUS then proceeds to format the Hard Disk with the specified parameters. While it is formatting PLUS displays the Operation in progress, the Cylinder & Head No. that is being formatted.

You could always hit <ESC> key to abort the format operation.

#### 2.0 Auto Interleave Option - (Destructive Operation)

This is the most powerful feature which enables you to get the peak performance out of your Hard Disk.

With this feature you need not speculate about the value of the Interleave Factor. PLUS is entrusted with the job of finding the optimum Interleave value by a trial & error method & formatting the Hard Disk with this value.

Discover the big advantage with this feature.

#### 3.0 Media Analysis Option - (Destructive Operation)

Media analysis performs the following operations on the Hard Disk:

- Preformats the Hard Disk with specified parameters like Format Option.

- Analysis the surface of the Hard Disk for any errors & makes a note of them.

- Marks the Bad Patches.

This takes quite some time & for best results this test should run uninterrupted.

The parameters required for this are to be inputted in the same way like the Format Option.

# a) Drive Type Definition

The default value for the drive type is the SETUP value set during the CMOS setup.

However if the drive was not set during CMOS Setup, the user now has an option of setting the drive to be one among the 46 standard Disk drive types.

Note that all the information about the drive unfolds when the disk drive type is being chosen.

If the disk drive type does not fall within the 46 standard disk types, use the USER option to define your own parameters for the drive.

Note that this USER definition is valid only as long as the Diagnostics is in effect. This feature is provided for you to test a disk drive, the definition for which is not available in the ROM.

## b) Interleave Factor

Choose an optimum interleave factor. Refer to the Appendix - A for details on how to decide on an Optimum interleave.

The default value for the interleave factor is 3.

#### c) Mark Bad Tracks

If the manufacturer has defined certain bad patches on the disk, enter <Y> to this question.

The user then goes into a menu which allows for complete editing of the bad track list.

Exit Bad track entry by hitting <ESC> or selecting the Save And Exit option. Note the usage of <ESC> key here.

The default answer for this question is <N>.

#### d) Cylinder Number

Enter the Start & End Cylinder Number if you want to override the defaults.

The same is true for Start & End Head number.

The default value for the start Cylinder & Head is 0 and that of the End cylinder & head is the value of the maximum cylinder & head respectively.

### e) Proceed

If all the entries are correct, you could hit <Y>. Else you could say <N> & go over all the entries again.

The default answer is <N>.

#### f) Warning

If you had hit <Y> to the previous question, you get a WARNING message. You could proceed to format if you are absolutely sure about the information you have entered upto this point.

#### g) Activity Screen

PLUS then proceeds to format the Hard Disk with the specified parameters. While it is formatting PLUS displays the Operation in progress, the Cylinder & Head No. that is being formatted.

You could always hit <ESC> key to abort the format operation.

#### 2.0 Auto Interleave Option - (Destructive Operation)

This is the most powerful feature which enables you to get the peak performance out of your Hard Disk.

With this feature you need not speculate about the value of the Interleave Factor. PLUS is entrusted with the job of finding the optimum Interleave value by a trial & error method & formatting the Hard Disk with this value.

Discover the big advantage with this feature.

### 3.0 Media Analysis Option - (Destructive Operation)

Media analysis performs the following operations on the Hard Disk:

- Preformats the Hard Disk with specified parameters like Format Option.

- Analysis the surface of the Hard Disk for any errors & makes a note of

- Marks the Bad Patches.

This takes quite some time & for best results this test should run uninterrupted.

The parameters required for this are to be inputted in the same way like the Format Option.

#### 4.0 Performance Test - (Non-Destructive Operation)

This test enables the user to check out his disk performance. The critical factor in deciding the disk performance is the Interleave Factor. Changing the Interleave factor can bring about drastic changes in Disk Performance.

-This test determines the Data Transfer Rate & the Track to Track Seek time. Data Transfer Rate is measured in the units Kilobytes/Second & the Track to Track seek time in milliseconds.

Higher value for Data transfer rate implies a better disk performance & lower value of track to track seek time indicates a better disk.

Refer to Appendix A for more on Interleave Factor & how to choose the same for best Disk Performance.

# 5.0 Seek Test - (Non-Destructive Operation)

This test checks the seek capability of the HardDisk on the specified Cylinder & Head range. First a sequential seek is performed & then a random seek is performed.

Any errors during this test are reported.

#### 6.0 Read/Verify Test - (Non-Destructive Operation)

This test performs sequential & random read & verify operation on the specified Cylinder, Head range.

#### 7.0 Force Bad Tracks - (Destructive Operation)

This operation enables an User to define a set of tracks as bad. Certain specific applications require this option.

#### Floppy Diagnostics

All the options under floppy diagnostics require more or less the require the following inputs:

- a) Drive No.

- b) Start Track No.

- c) End Track No.

As in the case of hard disk the list below gives the effect of each of the diskette tests:

a) Diskette Format

- Destructive.

b) Speed Test

- Non-destructive.

c) Random R/W Test

- Destructive.

d) Sequential R/W Test

- Destructive.

e) Disk Change Line Test - Non-destructive.

# 1.0 Diskette Format - (Destructive)

This test allows an user to check out the NEC 765 controller's abilities to format a diskette.

The user need not be bothered about the drive or the diskette in the drive. PLUS automatically determines the best way a diskette can be formatted for reliability. e.g. In case of a 1.2MB drive the user need not specify whether the diskette to be formatted is 1.2 MB or 360 KB capacity. PLUS finds the most reliable format automatically.

Note that this test does not write a DOS format on the diskette.

### 2.0 Drive Speed Test - (Non-destructive)

This test determines the speed of rotation of the drive. Please note that the following are the allowable speeds for the various drives:

a) 1.2 MB drive

-360 rpm for a 1.2 Mb diskette in it.

-300 rpm for a 360 Kb diskette in it.

b) 360 KB drive

-300 rpm.

c) 720 KB drive

-300 rpm.

Allow for a tolerance of 1% on all the speeds.

Ensure that the diskette is formatted before performing this test.

# 3.0 Random Read/Write Test - (Destructive)

This test performs a random read/write operation on the diskette & thus checks out the random seek capability of the drive.

-Again ensure that the diskette is formatted before performing this test.

# 4.0 Sequential Read/Write Test - (Destructive)

This test performs a Sequential read/write operation & checks out the sequential seek, read & write capability of the drive.

This test requires a formatted diskette.

5.0 Disk Change Line Test - (Non-destructive)

This test is valid only for drives with the disk change line feature namely

- 1.2 Mb drive

- 720 Kb or 3 1/2" drive.

This test checks whether the status of the disk change line changes when the diskette is removed/inserted in the drive.

This test requires a formatted diskette.

# Keyboard Diagnostics

There are two types of diagnostics performed on the keyboard/keyboard controller.

### They are:

- a) Controller Test.

- b) Scan/ASCII Code Test.

#### 1.0 Controller Test

This test exercises the keyboard controller & the keyboard status flags & takes about 2 minutes. Any error resulting from this test is reported.

Observe the CAPS, NUM & SCROLL LED's going on & off during the course of this test.

# 2.0 Scan / ASCII Code Test

Upon invoking this test a keyboard layout is shown on the screen. This keyboard layout might not necessarily correspond with your keyboard.

The objective of this test is to determine whether the keys depressed match with their scan code.

Thus every time a key is depressed the scan code & the ASCII code of the key is shown.

Use <CNTRL><BREAK> key to abort this test.

Function keys 11 & 12 in an Enhanced keyboard cannot be checked out by this test.

# Video Diagnostics

Video diagnostics includes the following:

- a) Sync Test

- b) Adapter Test

- c) Attribute Test

- -memory.

- d) 80 x 25 Display Test the display adapter.

- Checks the Sync capability.

- Performs test on the Display Memory.

- Checks the attributes of the Display

- Checks the 80 x 25 character set of

The video diagnostics requires very little input & the results can be visually observed.

### Miscellaneous Diagnostics

This includes the following tests:

- a) Serial Communication Port Test.

- b) Printer Port Test.

# 1.0 Serial Communication Port Test

This test requires a special RS-232C connector to be plugged on to the port.

The details of this connector are as below:

- RD & TD Shorted.

- DSR & DTR Shorted.

- CTS & RTS Shorted.

This test exercises the port for different:

- Baud Rates

- 7 Bit / 8 Bit &

- Odd / Even Parity

The results of the test are shown on the screen.

#### 2.0 Printer Port Test

This test writes a pattern on the Printer & the results are observed on the Printer.

#### Appendix A

#### 1.0 Interleave Factor - What is it?

To understand the meaning of Interleave associated with Hard Disks, we shall take you thru' an analogy. We hope we have made the meaning clear when we finish the analogy.

Consider the game of a roulette where a round table is set in motion & people wait for the motion to stop on their lucky number.

We shall add a slight twist to this game.

Assume we have 17 sectors on the roulette round table & that we have 17 coins numbered & stacked up in the order 1 thru' 17 with coin 1 at the top.

We shall now set the round table in motion at a reasonable speed & give ourselves the task of placing the coin from the stack pile on every sector taking the minimum time and remaining static at one place during the course of the game.

Assume you have placed coin I in a certain sector. By the time you pick up the next coin & place it, the immediate sector following coin I would have passed you. So what you would then do, is to place it on the sector just passing by.

Thus after placing the coins in all the sectors, you should stop the roulette table & look at coins numbers in the contiguous sectors.

You are sure to find that they are not in an increasing order. You soon realise that this disorder is due to the fact that the game requires you to place all the coins in minimum time.

If you had wanted the coins in an order, you would have had to wait for at least 17 revolutions before placing all the coins.

The average number of contiguous sectors between a sector occupied by coin 'n' & by coin 'n+1' can be termed as Interleave factor.

In this analogy the Hard Disk is the roulette table in motion at a constant speed of 3600 rpm & the person can be visualised as the head & the related data transfer hardware.

Information is organised in sectors & the sectors are accesed by their numbers. Thus using a specific interleave to number the sectors helps in achieving a data tansfer rate change.

For a Hard disk with factory specified access times, the only factor in the control of the user is the Interleave factor.

We realise this & we have the Auto Interleave feature which does exactly \_this.

as 2019, any emit-out to horse whereas a life also beening sout may serve

or not sections made and that the body to the plant that the william

Appendix - B

Please turn over for Appendix - B.

| Type | Cylinders | Heads | Write-precomp | Landing-zone | Capacity |

|------|-----------|-------|---------------|--------------|----------|

| 1    | 306       | 4     | 128           | 305          | 10 MB    |

| . 2  | 615       | 4     | 300           | 615          | 21 MB    |

| 3    | 615       | 6     | 300           | 615          | 31 MB    |

| - 4  | 940       | 8     | 512           | 940          | 64 MB    |

| 5    | 940       | 6     | 512           | 940          | 48 MB    |

| 6    | 615       | 4     | NONE          | 615          | 21 MB    |

| 7    | 462       | 8     | 256           | 511          | 31 MB    |

| 8    | 733       | 5     | NONE          | 733          | 31 MB    |

| 9    | 900       | 15    | NONE          | 901          | 115 MB   |

| 10   | 820       | 3     | NONE          | 820          | 21 MB    |

| 11   | 855       | 5     | NONE          | 855          | 36 MB    |

| 12   | 855       | 7     | NONE          | 855          | 51 MB    |

| 13   | 306       | 8     | 128           | 319          | 21 MB    |

| 14   | 733       | 7     | NONE          | 733          | 44 MB    |

| 15   | 000       | 0     | 000           | 000          | 00 MB    |

| 16   | 612       | 4     | ALL CYLS.     | 663          | 21 MB    |

| 17   | 977       | 5     | 300           | 977          | 42 MB    |

| 18   | 977       | 7     | NONE          | 977          | 58 MB    |

| 19   | 1024      | 7     | 512           | 1023         | 61 MB    |

| 20   | 733       | 5     | 300           | 732          | 31 MB    |

| 21   | 733       | 7     | 300           | 732          | 42 MB    |

| 22   | 733       | 5     | 300           | 733          | 31 MB    |

| 23   | 306       | 4     | ALL CYLS.     | 336          | 10 MB    |

| 24   | 925       | 7     | ALL CYLS.     | 925          | 56 MB    |

| 25   | 925       | 9     | NONE          | 925          | 72 MB    |

| 26   | 754       | 7     | 754           | 754          | 46 MB    |

| 27   | 754       | 11    | NONE          | 754          | 72 MB    |

| 28   | 699       | 7     | 256           | 699          | 42 MB    |

| 29   | 823       | 10    | NONE          | 823          | 71 MB    |

| 30   | 918       | 7     | 918           | 918          | 55 MB    |

| 31   | 1024      | 11    | NONE          | 1024         | 98 MB    |

| 32   | 1024      | 15    | NONE          | 1024         | 133 MB   |

| 33   | 1024      | 5     | 1024          | 1024         | 44 MB    |

| 34   | 612       | 2     | 128           | 612          | 10 MB    |

| 35   | 1024      | 9     | NONE          | 1024         | 80 MB    |

| 36   | 1024      | 8     | 512           | 1024         | 71 MB    |

| 37   | 615       | 8     | 128           | 615          | 42 MB    |

| 38   | 987       | 3     | 987           | 987          | 25 MB    |

| 39   | 987       | 7     | 987           | 987          | 60 MB    |

| 40   | 820       | 6     | 820           | 820          | 42 MB    |

| 41   | 977       | 5     | 977           | 977          | 42 MB    |

| 42   | 981       | 5     | 981           | 981          | 42 MB    |

| 43   | 830       | 7     | 512           | 830          | 50 MB    |

| 44   | 830       | 10    | NONE          | 830          | 72 MB    |

| 45   | 917       | 15    | NONE          | 918          | 115 MB   |

| 46   | 000       | 00    | 000           | 000          | 00 MB    |

# AMI-386XT SERIES-4 MANUAL

American Megatrends, Inc. Ph. (404) 263-8181 4025 Pleasantdale Road Suite 350, Atlanta, GA 30340

# **CONTENTS**

Introduction to The Manual

Section - 1 Unpacking and Installation

Section - 2 BIOS Overview

Section - 3. System Overview

Section - 4 Technical Specifications

Section - 5 I/O Channel & Connector Specifications

Section - 6 Advanced ROM Diagnostics

# Important Notice

AMI is not responsible for any errors or omissions in writing this manual. AMI reserves the right to change, modify or append any part or section of this manual at any time.

# Introduction to The Manual

| Section - 1 |   | It is essential to go through this section and follow the instructions for proper installation of the board.                                                              |

|-------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section - 2 | 5 | It is essential to go through this section to familiarize yourself with the AMI-386 BIOS.                                                                                 |

| Section - 3 |   | You are advised to go through this section to familiarize yourself with the motherboard.                                                                                  |

| Section - 4 |   | You may skip this section unless you need detailed technical information. All port descriptions required for personalized software development are given in this section. |

| Section - 5 |   | You may skip this section if you are familiar with the IBM AT <sup>1</sup> I/O Channel and Connector Specifications.                                                      |

| Section - 6 |   | Read this section to get the information about the built-in Advanced Diagnostics features.                                                                                |

|             |   |                                                                                                                                                                           |

$<sup>^{\</sup>mbox{\scriptsize I}}$  IBM AT is a registered trademark of International Business Machine Corporation.

# SECTION - 1

# Unpacking and Installation

# 1.1 Unpacking the AMI-386XT Motherboard

Your AMI-386XT motherboard contains sensitive electronic components, which can be easily damaged by static electricity.

In this section, we describe the precautions you should take while unpacking, as well as during installation. It is very important that the instructions be followed correctly, to avoid static damage, and to successfully install the board.

- 1) The motherboard should be left in its original packing until the time when it is to be installed.

- 2) Unpacking and installation should be done on a ground connected anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

- (A cheaper solution is to use a sheet of conductive aluminum foil grounded through a 1 Mega-ohm resistor, instead of the anti-static mat. Similarly, a strip of conductive aluminum foil wrapped round the wrist and grounded through a 1 Mega-ohm resister will serve the purpose of a wrist-band.)

Inspect the cardboard carton for obvious damage. In case damage is detected, call us, we are ready to help you.

Inside the carton, the card is packed in an anti-static bag, and sandwiched between sheets of sponge. Remove the sponge and lift out the anti-static bag with the card. Extract the card and place it ONLY ON A GROUNDED ANTI-STATIC SURFACE component side up.

Save the original packing materials, in case the card has to be shipped again. Shipping it in any other type of packing may damage the card.

Again inspect the card for damage. Press down all the ICs mounted on sockets to make sure they are properly seated.

DO NOT APPLY POWER TO THE BOARD IF IT HAS BEEN DAMAGED.

You are now ready to install your AMI-386XT motherboard.

Section 1

# 1.2 Installing the AMI-386XT motherboard.

Mounting the Motherboard in the chassis.

Before attempting to mount the board in the chassis, take a look at Fig.I to aquaint yourself with the locations of stand-offs and mounting screws. (Stand-offs and mounting screws are supplied with the chassis and NOT WITH THE MOTHERBOARD.)

Note: The mounting hole pattern on AMI-386XT motherboard is interchangable with that of the IBM AT/XT motherboard. It is assumed that the chassis is designed for standard IBM AT/XT motherboard mounting.<sup>1</sup>

CAUTION: During mounting and installation static protection is to be maintained as during unpacking.

Place the chassis on the anti-static mat and remove the cover. Take the plastic clips, nylon stand-offs and screws, for mounting the motherboard, and keep them separate. (Look into the chassis manufacturers booklet for instructions.)

The chassis has to be connected to ground to avoid static damage to the board, while mounting. To ground the chassis, connect an alligator clip with a wire lead to any unpainted part of the chassis. Ground the other end of the lead at the same point as the mat and the wristband. Rotate the chassis so that the front is to your right and the rear to your left. The side facing you is where the motherboard is to be mounted and the power supply will be mounted on the far side.

Take the four nylon stand-offs and push them into the holes provided for them in the motherboard ( see Fig. I ) from the solder side. The stand-offs will lock in place.

On the chassis, locate the slots where the stand-offs go in. Now, hold the motherboard (component side up) with the edge with three stand-offs towards you, and the edge with no stand-offs, away from you. (The edge connectors on the motherboard, for the adaptor cards, should be on your left.) Carefully slide the board into the chassis, making sure that the stand-offs go into the slots provided for them (see Fig. II). If the stand-offs are properly locked, the board should not slide right or left (forwards

<sup>&</sup>lt;sup>1</sup> IBM AT is a registered trademark of International Business Machine Corporation.

and backwards with respect to the chassis ) and should be level with the chassis. The far edge of the board should fit into the slots in the plastic clips. In case the board is not sitting properly, SLIDE IT OUT COMPLETELY and try again.

Now, put fhe two motherboard mounting screws in the holes provided for them (Fig. I) and tighten them. (You may have to shift the board slightly to align the screw mounting holes on the motherboard with those on the chassis.)

Now that the motherboard is properly mounted, the connectors have to be put in and the option jumpers and DIP switches set to your requirement.

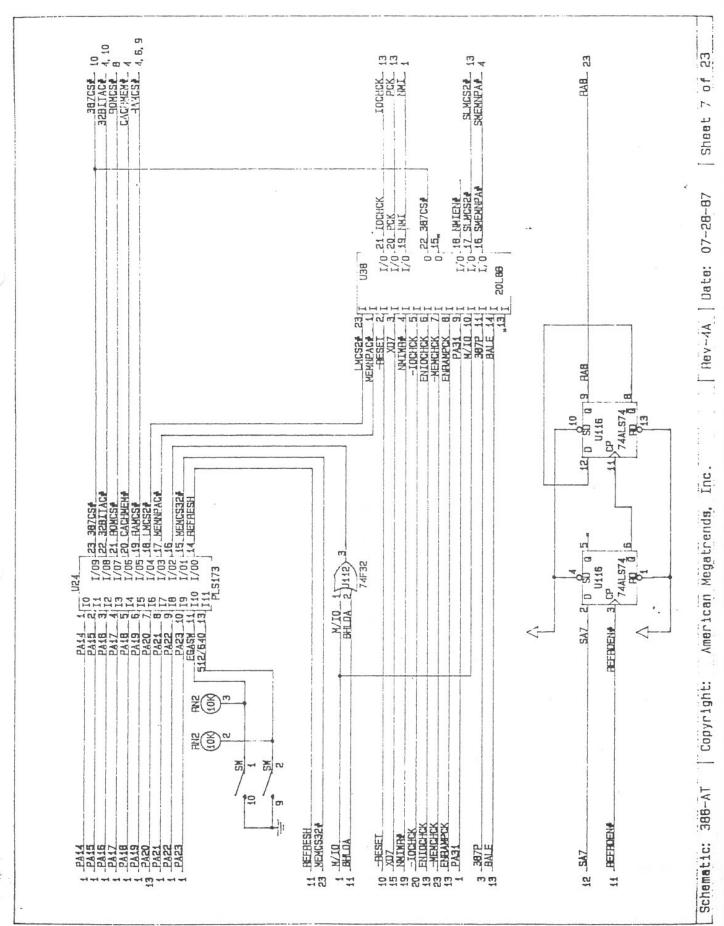

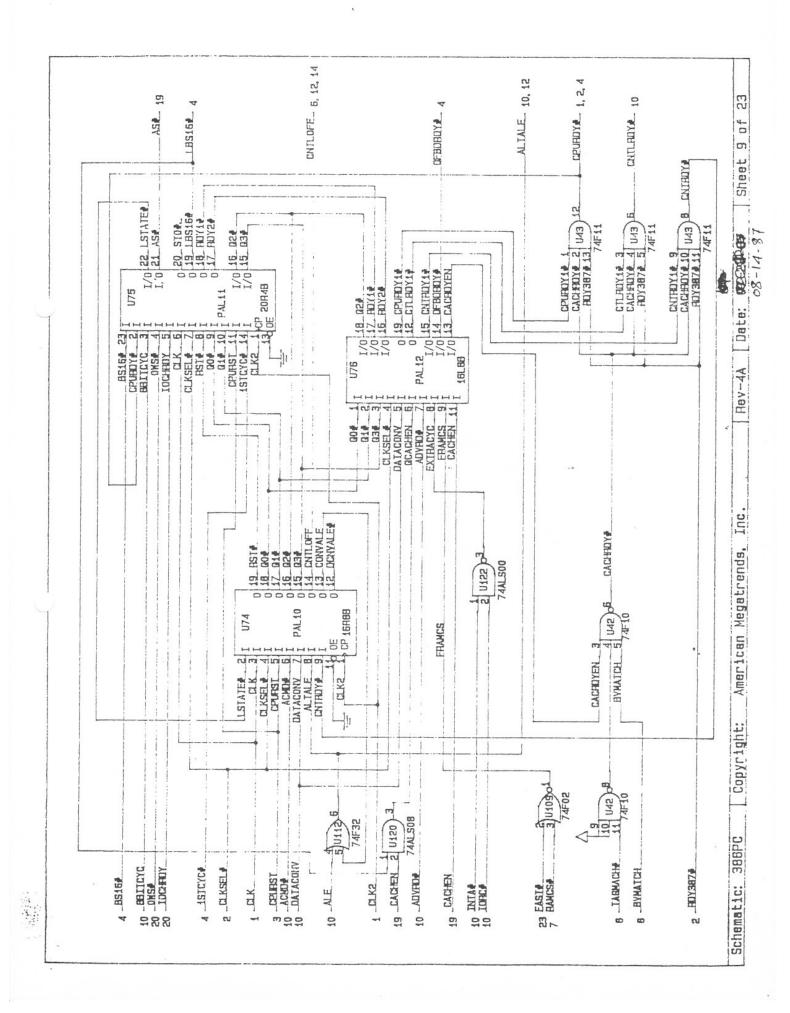

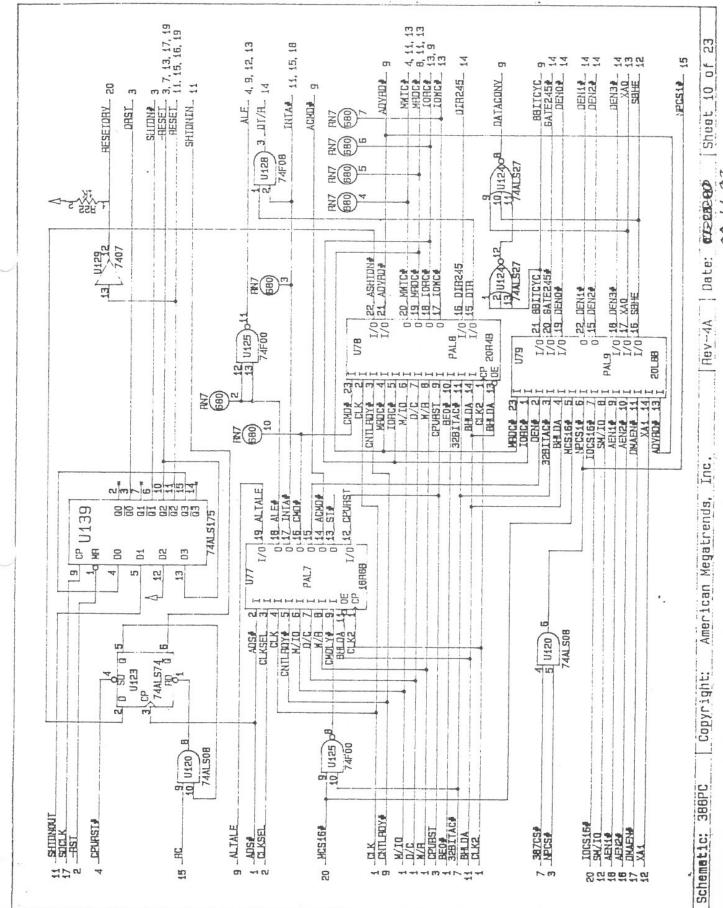

Figure III gives you the positions of the connectors, the option jumpers and the DIP switches on the card. The following table describes the options that can be selected.

NOTE: The options are factory set to the default selections and these options are indicated in the table by underscoring.

# 1.3 List of Jumper Options and Switch Settings for AMI-386XT

JI: TURBO LED

J2: 2 pin BERG strip

When shorted gives hard reset to the system

J4: 3 pin single in line . Short 1-2 if using 32K X 8 EPROM's (eg. 27256) Short 2-3 if using 16K X 8 or 8K X 8 EPROM's (eg 27128 or 2764)

J19: 4 pin single-in-line BERG Speaker Connector

J20: 5 pin single-in-line BERG

Keyboard Lock Connector

J21: 4 pin single-in-line BERG

Battery Connector for RTC/CMOS

J22: 5 pin DIN socket Keyboard Connector

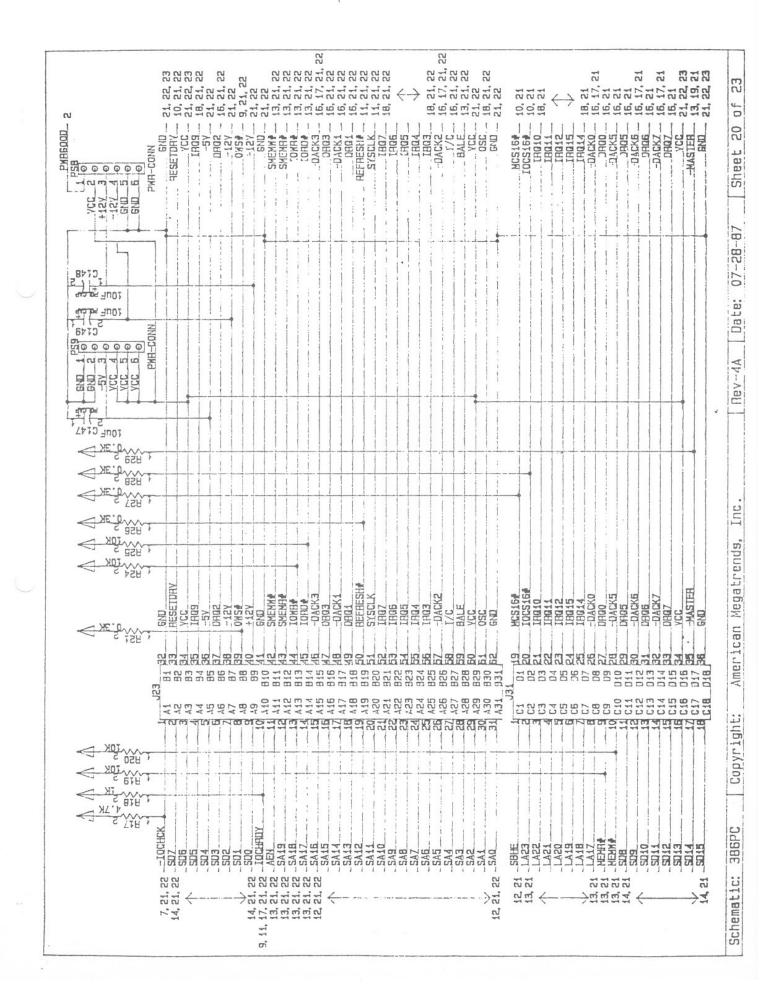

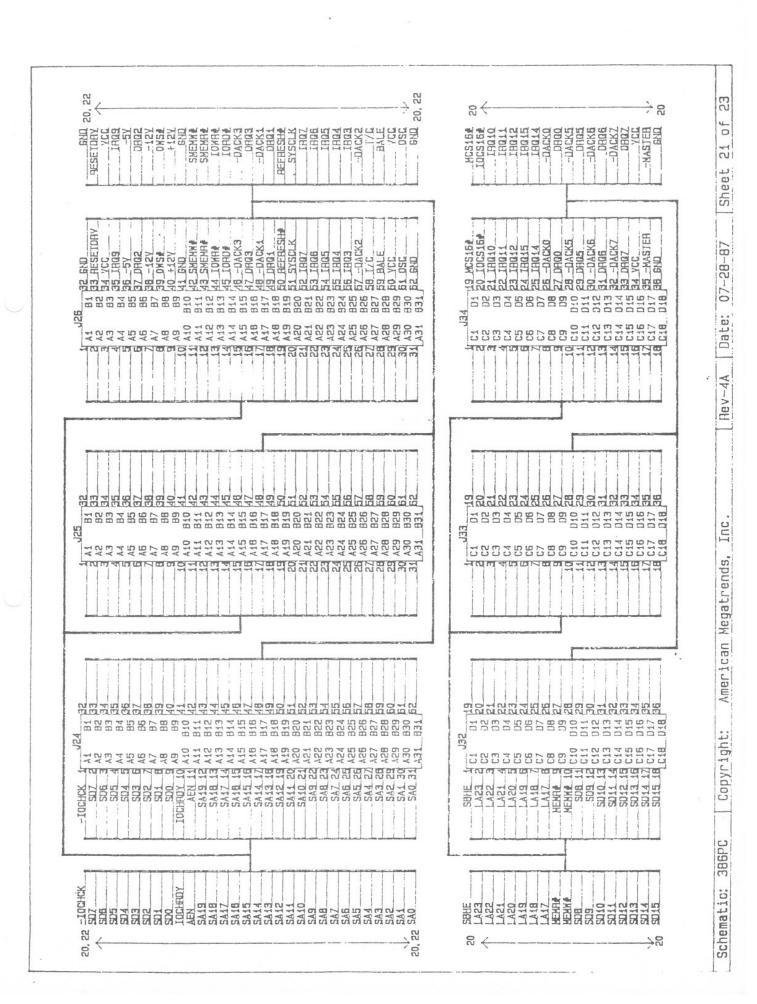

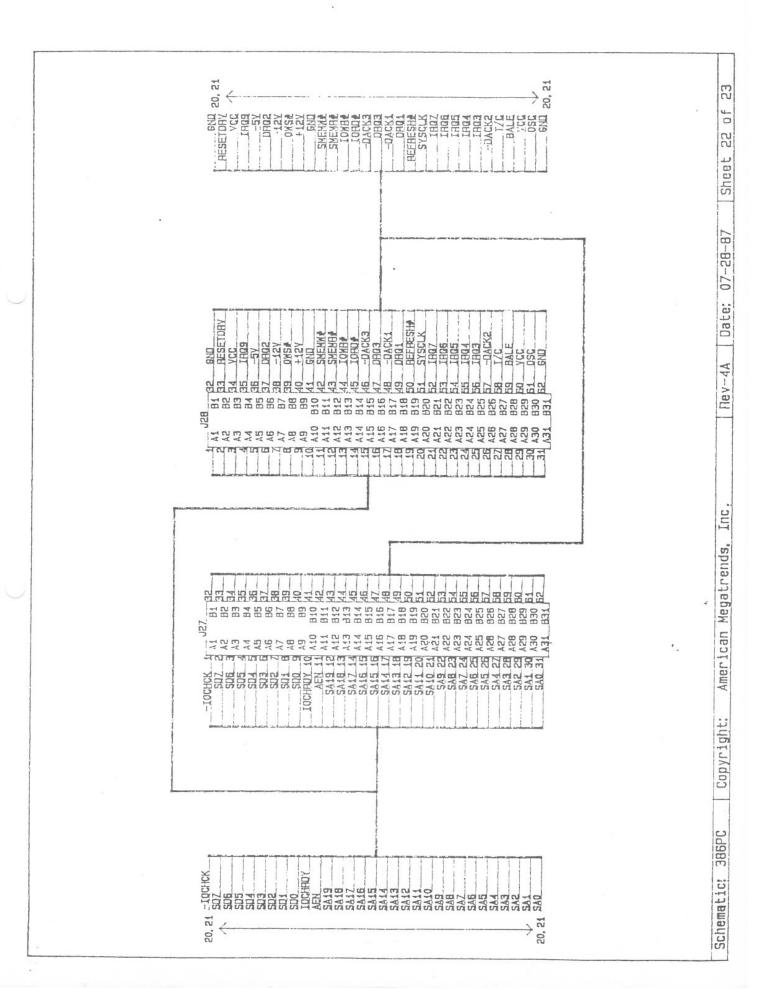

J23-28: 62 pin I/O Connectors

J31-34: 36 pin I/O Connectors

### Section 1

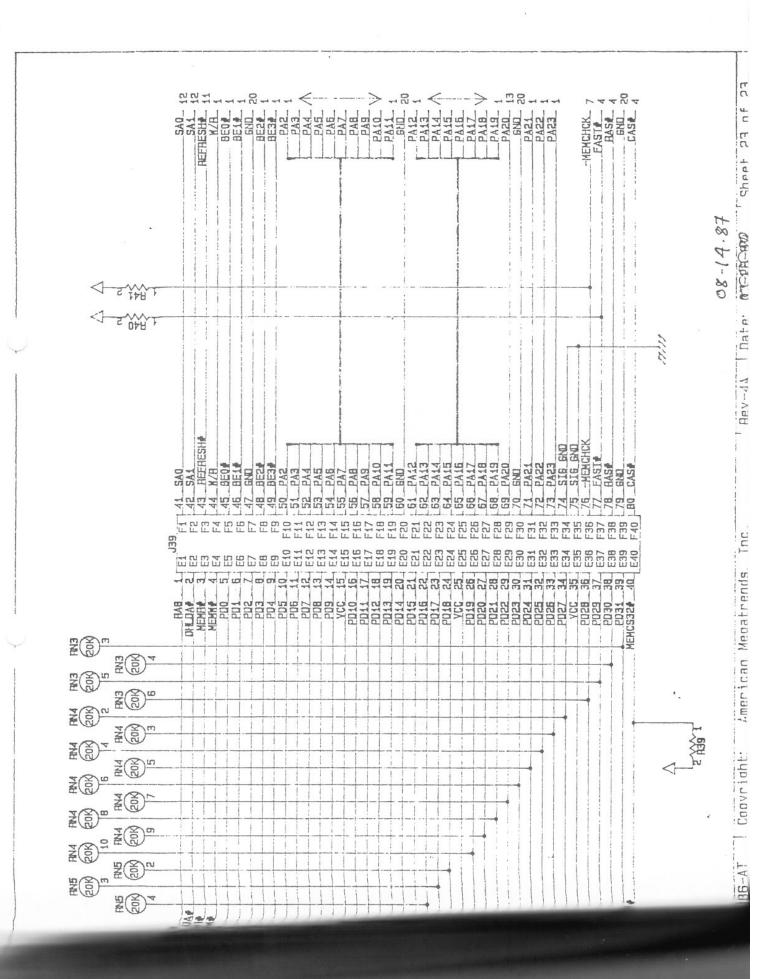

J39: 80 pin I/O Connector for 32 bit memory

PS8-9: 6 pin Power Supply Connectors

SW: 5 bit slide switch

| 5 | Video adapter card option        |

|---|----------------------------------|

| 4 | Power on system clock frequency  |

| 3 | Numeric processor option         |

| 2 | 512k to 640k cache on/off option |

| 1 | On hoard EGA BIOS option         |

|                                                                                                                                                                                | ON-BOARD EGA BIOS OPTION                                                                                                                |                                |                                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------|--|

| SWI                                                                                                                                                                            | ON/OF                                                                                                                                   | F EPROM MAP                    | DESCRIPTION                              |  |

|                                                                                                                                                                                | ON                                                                                                                                      | 0C0000-0C7FFF<br>0F0000-0FFFFF | On Board EGA BIOS enabled(32 bit access) |  |

|                                                                                                                                                                                | OFF                                                                                                                                     |                                | BIOS On EGA Card selected(8 bit access)  |  |

| 512K TO 640K CACHE ON/OFF OPTION  SW2 ON/OFF DESCRIPTION  ON If 512KB below 1MB option is selected memory card then 512KB to 640KB memory land to 640KB memory card if present |                                                                                                                                         |                                | N/OFF OPTION                             |  |

|                                                                                                                                                                                |                                                                                                                                         |                                | en 512KB to 640KB memory on the          |  |

|                                                                                                                                                                                | OFF If 512KB below 1MB option is selected memory card then 512KB to 640KB me I/O expansion BUS will not be cache memory will be cached. |                                |                                          |  |

|                                                                                                                                                                                | *******                                                                                                                                 |                                |                                          |  |

|                                                                                                                                                                                | 80387<br>OPTIO                                                                                                                          |                                | CESSOR PRESENT/NOT PRESENT               |  |

| SW3                                                                                                                                                                            | ON/OFF DESCRIPTION                                                                                                                      |                                |                                          |  |

| ON Numeric coprocessor physically not present board. This switch should always be on w numeric processor is not present.                                                       |                                                                                                                                         |                                | tch should always be on when the         |  |

OFF 80387 is physically present on the board.

#### Section 1

# POWER-ON SYSTEM CLOCK FREQUENCY SELECTION

# SW4 ON/OFF DESCRIPTION

ON POWER ON System clock frequency is 6MHz.

However the clock can be changed to 16 MHz

using keyboard clock switching option.

OFF POWER ON System clock frequency is 16MHz

# VIDEO ADAPTER CARD OPTION

### SW5 ON/OFF VIDEO ADAPTER CARD

-----

ON COLOR GRAPHICS CARD

OFF MONOCHROME DISPLAY ADAPTER

# C35: Variable Capacitor

The system board has a variable capacitor. Its purpose is to adjust the 14.31818 MHz oscillator (OSC) signal that is used to obtain the color burst signal required for color televisions.

### MEMORY BOARD SWITCH SETTING

| SWITCH | OPTION                              | STATE     | DESCRIPTION                                                    |

|--------|-------------------------------------|-----------|----------------------------------------------------------------|

| SW1    | BANK SELECT                         | ON<br>OFF | Two 32bit memory bank present<br>One 32bit memory bank present |

| SW2    | MEMORY SIZE<br>BELOW 1MB            | ON<br>OFF | 640K below 1MB<br>512K below 1MB                               |

| SW3    | 384KB MEMORY<br>ABOVE 1MB OR<br>2MB |           | Enable<br>Disable                                              |

# SECTION 2 BIOS Overview

This guide explains how to:

- a) Install the AMI-386 BIOS on the AMI-386 Motherboard.

- b) Use the built-in Set-up Procedure.

- c) Select the Clock Speed / Wait States through the Keyboard.

- d) Interpret the errors reported by the AMI-BIOS.

- e) Use the 3 1/2" floppy drive support effectively.

#### 2.A Installing the AMI-386 BIOS

Skip this paragraph if the BIOS is already plugged on the AMI-386XT Board.

Before you begin the installation ensure the following:

- i) The Board is powered down.

- ii) ROM's are susceptible to static electricity. So observe the following precautions when you handle a ROM:

- a) Unpack the ROM's on a ground connected anti-static mat.

- b) Wear an anti-static wristband, grounded at the same point as the anti-static mat.

(A cheaper solution is to use a sheet of conductive aluminium foil grouded through a 1 Mega-ohm resistor instead of an anti-static mat. Similarly, a strip of conductive aluminium foil wrapped around the wrist and grounded through a 1 Megaohm resistor will serve the purpose of a wrist band.)

Now follow the steps below:

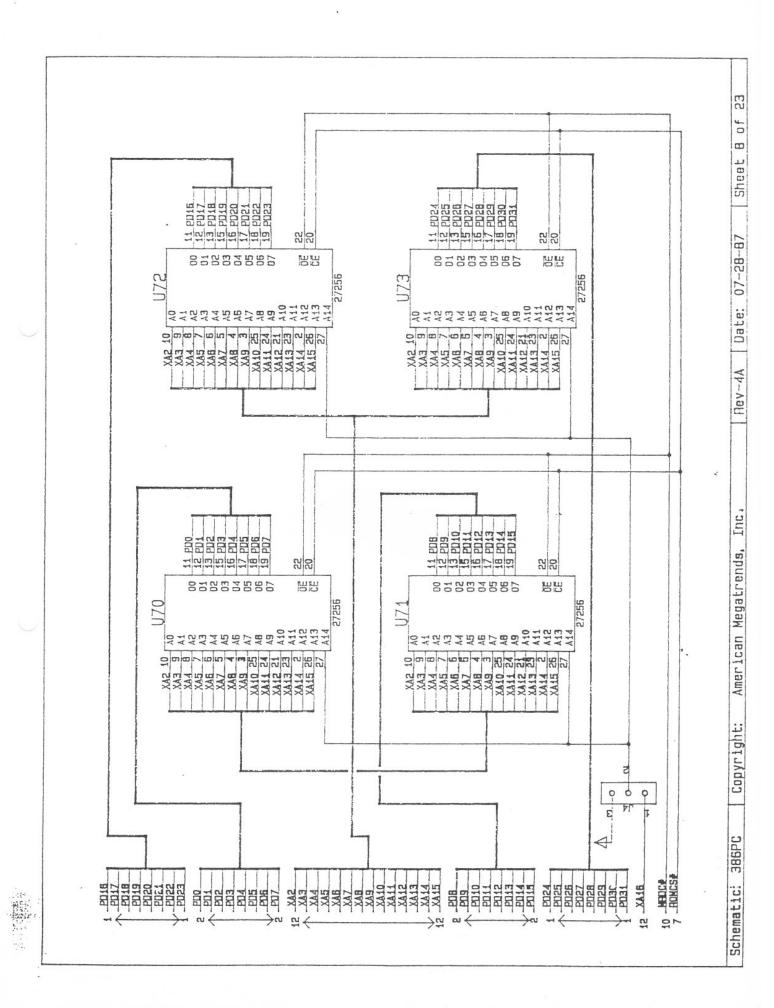

- Unpack the ROM's and identify the Labels 386-0, 386-1, 386-2 and 386-3.

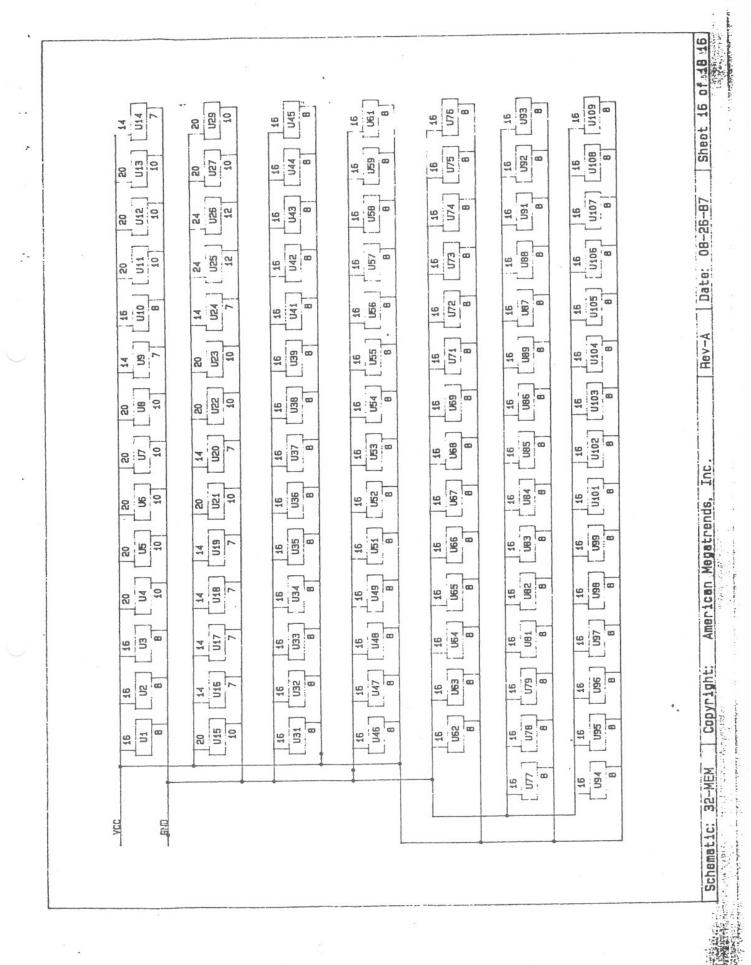

- Locate the IC Sockets U70, U71, U72 and U73 on the 386 Motherboard.

- Plug in the following order:

- ROM with label 386-0 in U70 socket,

- ROM with label 386-1 in U71 socket,

- ROM with label 386-2 in U72 socket,

- ROM with label 386-3 in U73 socket.

When you do these make sure that the notch on the ROM is facing away from the I/O connector.

#### 2.A.1 Starting Up The System

Follow the procedure recommended in Section 1 of the Hardware manual.

Power up the system and wait for the BIOS to show up the BIOS activity on the screen.

#### 2.A.2 Memory Test Bypass

The BIOS performs diagnostics of the system and displays the size of the memory being tested.

Note that you can bypass the memory test by pressing the <ESC> key. This option would be quite useful when the memory on the system is quite large. You should hit the <ESC> key when the message Press <ESC> Key to bypass MEMORY test appears on the screen.

Also note the Ref. number at the bottom of the screen. Make a note of this number before you call Customer Support at AMI for assistance with the BIOS.

#### Cache Test

The 386-BIOS as a part of its diagnostics tests the cache memory. The BIOS also displays the size and status of the cache memory on the screen. This display can be seen on the second line just past the memory size display.

The size of the cache memory is usually 64 KB. In case the cache memory is found bad then the BIOS alarms the user with the following message:

#### CACHE MEMORY BAD - DO NOT ENABLE CACHE

Refer to Section 2.C for more information about enabling/disabling cache. The discussion on the advantages of cache can be found in the Hardware section 3.1.

#### 2.B CMOS Setup

Immediately after the memory and cache test, you will get the following prompt on the screen:

Press <DEL> key to run SETUP Utility

Hit <DEL> key to get into the Setup, Mode. Note that <DEL> key will get you into the set-up mode only when the message:

Press <DEL> key to run SETUP Utility, is displayed on the screen.

If you hit <DEL> key the following message appears on the screen: WANT TO RUN SETUP UTILITY (Y/N)?

If you hit <Y> or <y> and the <ENTER> key you have the Setup screen.

2.B.1 Time/Date Setup

The Setup screen looks like below:

CMOS SETUP Curret date is: XX-XX-XXXX Enter new date (MM-DD-YYYY)?

To this question you would have to enter the date in the format shown on the screen.

If you feel that the current date should remain unchanged, you would just have to hit the <ENTER> key. In such a case the new date is set to the same value as the current date.

The next question you have on the screen is:

Current time is :XX:XX:XX Enter new time (HH:MM:SS)?

To this question you key in the time in the format defined. Press <ENTER> key alone if the current time is right.

As soon as you have done this the BIOS shows you the type of the display on your system.

After that, the setup takes two differet paths depending upon the CMOS being initialized or uninitialized.

#### 2.B.2 CMOS Initialized

Under these conditions you would see the following messages:

Fixed disk drive C type : X (if installed else Not Installed.)

Fixed disk drive D type : X (if installed else Not Installed.)

Diskette drive A is 3 1/2"

Diskette drive B is : Double Sided (Other options as above)

Base Memory Size is : XXX KB

Expansion memory size is : XXXX KB

Are these options correct (Y/N)?

Note that the information about Drive A indicates 3 1/2", as CMOS had been set earlier to reflect this status. If on the contrary, CMOS had been set for a 1.2 MB drive, the message in place of 3-1/2" it would be High Capacity.

If you feel that the information displayed above is right, hit <Y> and the <ENTER> key to proceed to system boot with the new information.

#### 2.B.3 CMOS Uninitialised

#### 2.B.3.1 Disk Drive Type Definition

In this case you would have to enter the type of the fixed Drive C in response to the message:

#### \*\*\*\* WARNING \*\*\*\*

Entering the wrong disk drive TYPE causes improper operation of the disk. If disk not installed press <RETURN> For disk TYPE details press <ESC>

Enter disk drive C type (1-47)?

Note that the disk type details are only a key stroke away. Hit <ESC> key to find for yourself. You could always come back by hitting <ESC> again.

Once you have convinced yourself about the drive type enter the appropriate number and hit <ENTER>.

Note that pressing <ENTER> key alone indicates the absence of the Drive C.

You would then be asked to enter the type of the disk Drive D. The procedure for doing this is the same as that for Drive C. Remember if you do not have disk Drive D on your system, you just have to hit the <ENTER>

key.

2-5

Bright of the Sell one of the properties and the Sell one of the Sell of t

Section 2

| Type     | Cylinders | Heads | Write-precomp | Landing-zone | Capacity |

|----------|-----------|-------|---------------|--------------|----------|

| <br>1    | 306       | 4     | 128           | 305          | 10 MB    |

| 2        | 615       | 4     | 300           | 615          | 21 MB    |

| 3        | 615 =     | 6     | 300           | 615          | 31 MB    |

| 4        | 940       | 8     | 512           | 940          | 64 MB    |

| 5        | 940       | 6     | 512           | 940          | 48 MB    |

| 6        | 615       | 4     | NONE          | 615          | 21 MB    |

| 7        | 462       | 8     | 256           | 511          | 31 MB    |

| 8        | 733       | 5     | NONE          | 733          | 31 MB    |

| 9        | 900       | 15    | NONE          | 901          | 115 MB   |

| 10       | 820       | 3     | NONE          | 820          | 21 MB    |

| 11       | 855       | 5     | NONE          | 855          | 36 MB    |

| 12       | 855       | 7     | NONE          | 855          | 51 MB    |

| 13       | 306       | 8     | 128           | 319          | 21 MB    |

| 14       | 733       | 7     | NONE          | 733          | 44 MB    |

| 15       | 000       | 0     | 000           | 000          |          |

| 16       | 612       | 4     | ALL CYLS.     |              | 00 MB    |

| 17       | 977       | 5     | 300           | 663<br>977   | 21 MB    |

| 18       | 977       | 7     | NONE          |              | 42 MB    |

| 19       | 1024      | 7     |               | 977          | 58 MB    |

| 20       | 733       | 5     | 512           | 1023         | 61 MB    |

| 21       | 733       | 7     | 300           | 732          | 31 MB    |

| 22       | 733       | 5     | 300           | 732          | 42 MB    |

| 23       | 306       | 4     | 300           | 733          | 31 MB    |

| 24       | 925       | 7     | ALL CYLS.     | 336          | 10 MB    |

| 25       |           |       | ALL CYLS.     | 925          | 56 MB    |

|          | 925       | 9     | NONE          | 925          | 72 MB    |

| 26<br>27 | 754       | 7     | 754           | 754          | 46 MB    |

|          | 754       | 11    | NONE          | 754          | 72 MB    |

| 28       | 699       | 7     | 256           | 699          | 42 MB    |

| 29       | 823       | 10    | NONE          | 823          | 71 MB    |

| 30       | 918       | 7     | 918           | 918          | 55 MB    |

| 31       | 1024      | 11    | NONE          | 1024         | 98 MB    |

| 32       | 1024      | 15    | NONE          | 1024         | 133 MB   |

| 33       | 1024      | 5     | 1024          | 1024         | 44 MB    |

| 34       | 612       | 2     | 128           | 612          | 10 MB    |

| 35       | 1024      | 9     | NONE          | 1024         | 80 MB    |

| 36       | 1024      | 8     | 512           | 1024         | 71 MB    |

| 37       | 615       | 8     | 128           | 615          | 42 MB    |

| 38       | 987       | 3     | 987           | 987          | 25 MB    |

| 39       | 987       | 7     | 987           | 987          | 60 MB    |

| 40       | 820       | 6     | 820           | 820          | 42 MB    |

| 41       | 977       | 5     | 977           | 977          | 42 MB    |

| 42       | 981       | 5     | 981           | 981          | 42 MB    |

| 43       | 830       | 7     | 512           | 830          | 50 MB    |

| 44       | 830       | 10    | NONE          | 830          | 72 MB    |

| 45       | 917       | 15    | NONE          | 918          | 115 MB   |

| 46       | 000       | 00    | 000           | 000          | 00 MB    |

#### Diskette drive A is 3 1/2" (Y/N)?

The above question is asked if the drive has been found to have 80 tracks. Since a drive with 80 tracks could either be a

- high capacity i.e 1.2 MB drive

- or 3 1/2" i.e 720 KB drive,

you would have to answer this question.

By entering <N> or <n> you can select the high capacity drive. Alternatively enter <Y> or <y> to select a 720 KB drive. This question could come up for the case of drive B as well provided it has been detected as a 80 track drive by the BIOS.

If you hit the <ENTER> key alone, the BIOS assumes the drive to be a 1.2 MB drive.

At this point you have entered all the information the BIOS requires for starting up the system.

BIOS detects a few details by itself, e.g. the diskette drive type in case of a 360 KB drive as shown below:

Diskette drive B is : Double Sided (Other options as above)

Base Memory Size is : XXX KB

Expansion memory size is : XXXX KB

Are these options correct (Y/N)?

If you are convinced at this stage that all the information you have entered upto this point is right, hit <Y> or <y> key followed by <ENTER> key. When you do this the BIOS goes all over again to boot up the system with the information specified.

However, if you would like to modify some information, then you should hit either <N> or <n> key followed by enter. You would now go through the setup all over again.

#### 2.B.4 Summary of Set-up

The Set-up screen thus requires you to set

- a) Date.

- b) Time.

- c) Hard Disk Type For Drive C (if present).

- d) Hard Disk Type For Drive D (if present).

The Set-up procedure also automatically detects the following:

- a) Type Of Display Card.

- b) Size Of Real Memory.

- c) Size of Memory beyond 1 MB.

- d) Presence of 360 kb floppy drives.

- e) Presence of a 80387.

Also, if a second Hard Disk drive is physically connected but the CMOS is not set for this Drive D, the BIOS informs you about the same and gives you a chance to configure the drive through SETUP.

Having setup the CMOS, the BIOS runs through the diagnostics again, tests the memory, sets up the devices configured and proceeds to boot.

Note that the Set-up option is available even after a soft reset.

#### 2.B.5 When does the BIOS prompt you to run Set-up?

The BIOS prompts you to run Set-up under the following conditions:

- a) CMOS options not set.

- b) Display Configuration Mismatch.

- c) Memory Size mismatch.

- d) Hard Disk Set-up error.

- e) CMOS battery is low.

- f) An additional hard disk presence is detected.

#### 2.C Selecting Clock Speed/Wait States

AMI-BIOS allows you to change Clock Speeds and Wait States through the keyboard at any time. Following are the key combinations and their meanings :-

Key Combinations

Meaning 1. <CNTRL><ALT><÷> Switch to 16Mhz, 0 Wait State -

Block Cursor indicates the switch

2. <CNTRL><ALT><-> Switch to 6Mhz, 1 Wait State -

Double-line Cursor indicates the

switch over.

- 3. <CNTRL><ALT><L-SHIFT><+> Select Zero Wait State.(Enable Cache) - only at 16MHz.

- 4. <CNTRL><ALT><L-SHIFT><-> Select One Wait State.(Disable

At the time of diagnostics the BIOS tests the cache memory. If the cache test fails, the BIOS does not allow the user to enable cache through the key combination.

### 2.C.1 Default Settings for Clock and Cache

Note that the speed of the system after power-on can be set by a DIP switch SW7. The details of the same can be had under Section 1.3. If the switch is on, the system boots up at 6 MHz with the cache disabled. If it is off, the system boots up at 16 MHz with the cache enabled. If the power-on cache self-test fails, the cache is not enabled, even when the system boots at 16 MHz.

The system returns to this default state after soft reset (warm boot). Note that during a WARM boot the cache memory is not tested.

# 2.C.2 Low Level Programs for Clock/Cache Selection

The low level programs discussed below will have to be executed under DOS DEBUG program. The user should be familiar with low level programming before he/she attempts the programs given below.

a) Port Definitions: Clock and cache are selected using the following i/o ports:-

CLOCK selection port Address: 0461H CACHE selection port Address: 0460H

Bit Map: In case of both the ports mentioned above the LSB status (Least Significant Bit i.e BIT 0) determines the selection. The remaining 7 bits i.e BIT 1 thru BIT 7 are don't care.

B7 B6 B5 B4 B3 B2 B1 B0 X X X X X X X X LSB

Port 461 LSB: 0 -> 6 MHz 1 -> 16 MHz

Port 460 LSB: 0 -> Disable cache 1 -> Enable cache

- b) Selecting High or 16 MHz Speed: Under DEBUG prompt enter the following command:

-O 461,1 <ENTER>

- c) Selecting Low or 6 MHz Speed: Under DEBUG prompt enter the following command:

-O 461,0 <ENTER>

- d) Status Of Clock: Under DEBUG prompt enter the following command:

-I 461<ENTER>

XX

In response the port status is returned in XX. Looking at the LSB the clock speed can be found. If the LSB is set the speed is 16MHz else it is 6 MHz.

e) Enabling the Cache: Enable CACHE using the low level command shown below only after confirming that the cache is good. The As described earlier, the cache status is displayed by the BIOS after power-on.

Under DEBUG prompt enter the following command: -O 460 1<ENTER>

- f) Disabling the Cache: Under DEBUG prompt enter the following command:

- -O 460 0<ENTER>

- g) Status Of Cache: Under DEBUG prompt enter the following command: -I 460<ENTER> XX

In response the port status is returned in XX. Looking at the LSB the cache status can be found. If the LSB is set the cache is enabled else it is disabled.

#### 2.D Errors Reported By AMI-BIOS

AMI-BIOS performs various diagnostic tests at the time the system is powered up. Whenever an error is encountered during these tests, either you hear a few short beeps or see an error display on your monitor. If the error occurs before the display device is initialised the system reports the error by giving a number of short beeps.

If the error is FATAL then system halts after reporting the FATAL error. If the error is NON-FATAL the process continues after reporting the NON-FATAL error.

#### Fatal Errors

| Веер     | Count | Meaning                               |

|----------|-------|---------------------------------------|

|          | 1     | DRAM-refresh failure.                 |

|          | 2     | Parity Circuit failure.               |

|          | 3     | Base 64KB RAM failure.                |

|          | 4     | System Timer failure.                 |

|          | 5     | Processor Failure.                    |

|          | 6     | Keyboard Controller - Gate A20 error. |

|          | 7     | Virtual Mode Exception Error.         |

|          | 8     | Display Memory R/W Test Failure. (*)  |

|          | 9     | ROM-BIOS CheckSum Failure.            |

| 22333333 |       |                                       |

#### (\*) Non-Fatal Error.

#### Error Messages

#### Fatal Errors

- 1. Channel 2 of Timer Not functional.

- 2. Stray Interrupt sensed in controller.

- 3. Interrupt controller #2 not functional.

#### Non-Fatal Errors

- 1. Keyboard Error.

- 2. Keyboard/Interface Error.

- 3. CMOS battery state low.

- 4. CMOS system options not set.

- 5. CMOS checksum failure.

6. CMOS memory size mismatch.

7. CMOS system time and date not set.

- 8. CMOS display configuration mismatch.

- 9. Display setting not proper.

- 10. Keyboard is locked ..... Unlock it.

- 11. Floppy disk controller failure.

- 12. Hard disk unit 0 error.

- 13. Hard disk unit 1 error.

- 14. Hard disk unit 0 failure.

- 15. Hard disk unit 1 failure.

- 16. Hard disk unit 1 is not defined in CMOS.

- 17. Cache Memory Bad Do Not Enable Cache.

#### 2.E Use of 3 1/2" Support Effectively

DOS 3.20 provides support for 3 1/2" drives. For this purpose it needs support from the ROM BIOS. AMI-BIOS release date 12/03/86 onwards provides the necessary support.

#### · Section 2

The 3 1/2" drive can be freely configured as Drive A or Drive B with this BIOS. Thus it is possible to boot off directly from a 3 1/2" drive.

Earlier versions of DOS would require the use of DRIVER.SYS to provide the necessary support.

A few points would have to be kept in mind when you use the 3 1/2" drive and a 1.2 MB together. Ensure that when you perform the Setup you define the drives correctly. Incorrect definition could make the drive unusable.

The table below describes the valid combinations on a AT:

| CMOS Status      | Physical Dr      | ive Status Functiona | 1 |

|------------------|------------------|----------------------|---|

| 1.2 MB<br>3 1/2" | 1.2 MB<br>3 1/2" | YES<br>YES           | - |

| Undefined 1.     | 2 MB             | YES                  |   |

The remaining combinations are invalid. Please make a note of these combinations before you call us for help.

#### SECTION 3

# System Overview

#### 3.1 Description

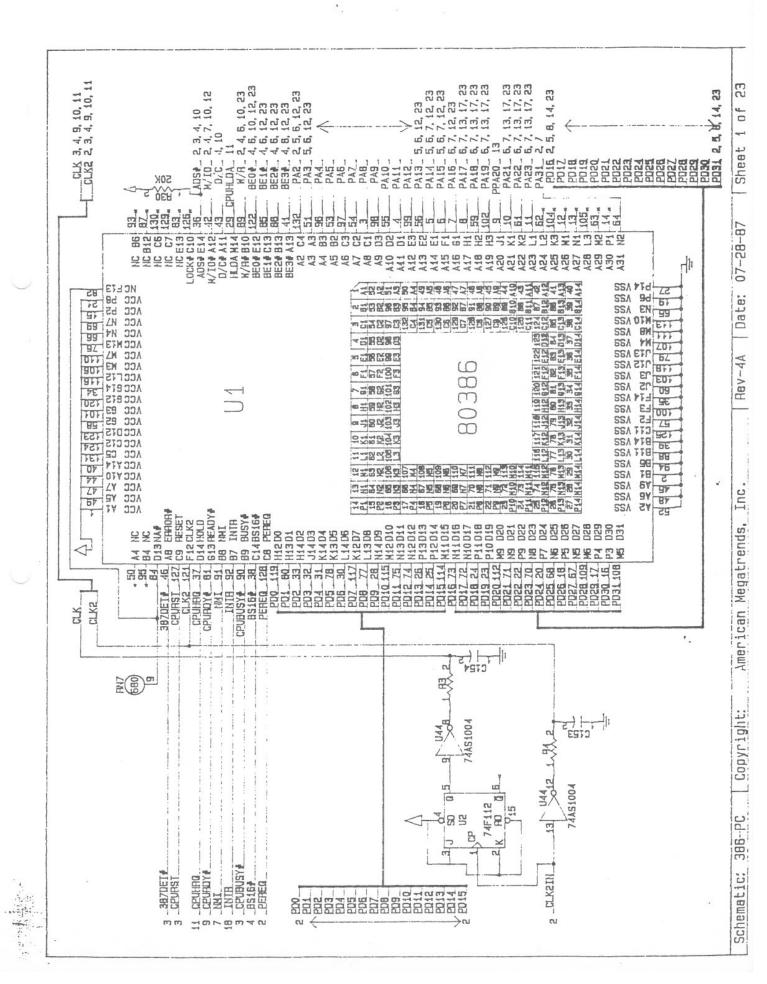

The system board is approximately 8.5 by 13 inches and uses very large scale integration (VLSI) technology. It has the following features:

- \* 80386 Microprocessor

- \* 16 MHz System Clock

- \* Optional 80387 Numeric Coprocessor (6/16MHz)

- \* System support function:

- -7 Channel Direct Memory Access (DMA)

- -16 level interrupt

- -Three programmable timers

- -System clock

- \* User selectable 64KB/128KB read only memory (ROM) subsystem

- \* 64KB Cache Memory which caches 16MB memory address space

- \* User selectable synchronized system board clock switching option for reducing the processor clock frequency to 6MHz

- \* 8MHz I/O bus timing compatibility at 16MHz board operation

- \* Speaker attachment

- \* Complementary Metal Oxide Semiconductor (CMOS) RAM to maintain system configuration

- \* Real-Time clock

- \* Battery backup for CMOS configuration table and Real-Time Clock

- \* Keyboard attachment

- \* 8.5 by 13 inch board: Extended XT 1 form-factor

- \* 6 input/output (I/O) slots:

- 4 with a 62 + 36 pin card-edge socket

- 1 with only the 62-pin card-edge socket

- 1 32bit memory slot

#### 3.2 The Microprocessor

The 80386 is a high performance 32-bit microprocessor designed for Multitasking soperating systems. The processor can address up to 4-Gigabytes of physical memory and 64-Terabytes (1-Terabyte = 1-K Gigabyte) of virtual memory (this design limits the physical address It has integrated memory management and protection to 16MB). architecture which includes address translation registers, advanced multitasking hardware and protection mechanism to support operating systems. In addition, it is object code compatible with 8086 family of microprocessor. The 80386 has built-in features to support coprocessors, DMA and interrupts (both maskable and non-maskable). It has two modes of operation: Real address mode and Protected virtual address mode.

In real address mode it operates as a fast 8086 with 32-bit extension if desired. In Protected mode, software can perform a task switch into tasks designated as virtual 8086 mode tasks. The virtual 8086 tasks can be isolated and protected from one another by the use of paging and I/O permission bit map.

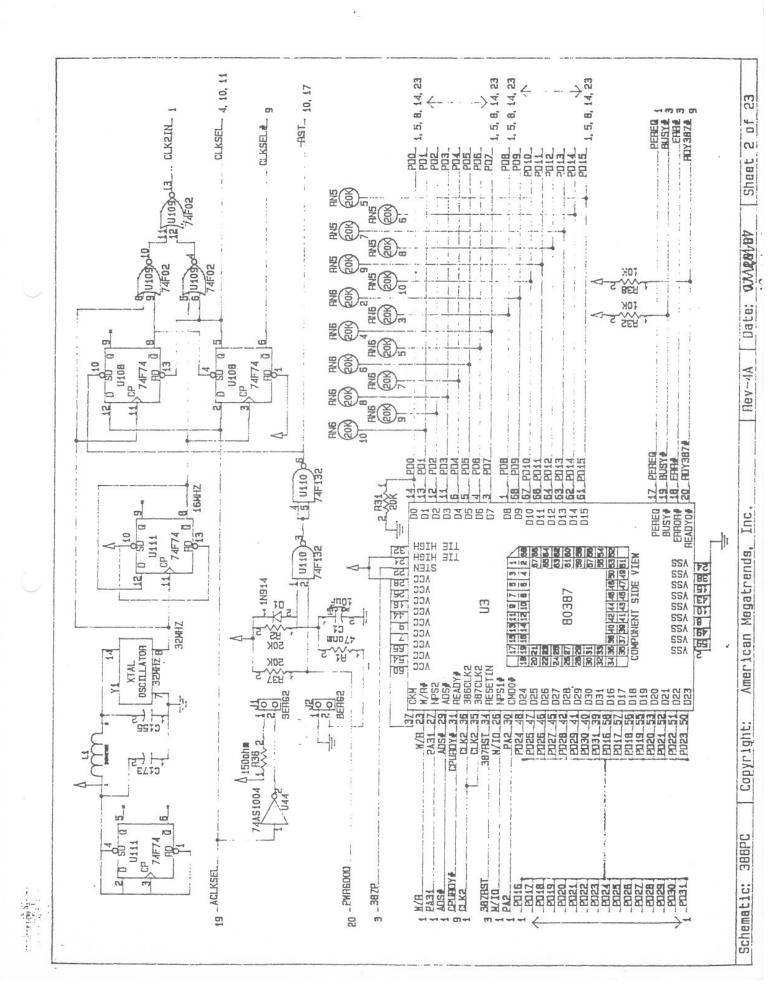

#### 3.3 System Performance

#### Clock Speed

The AMI-386XT can operate at 16MHz, which results in a clock cycle time of 62.5ns. It can run at two different clock rates. The lower clock speed is normally 6 or 8MHz. For convenience, we shall assume this speed to be 6MHz throughout the rest of this manual. If the oscillator U111 on the board is 16MHz instead of 12MHz, all the 6MHz timing will have to be reduced by 25%. Similarly, if Y1 is something other than 32MHz, the 16MHz timings will have to be appropriately rated.

The switch SW-4 determines the initial clock frequency after power-on. Refer to Section 1.3 for details. The clock speed can be switched at any time when the machine is operating. Refer to Section 2.C for details.

The 80387 Numeric processor runs at the processor clock frequency.

#### Data Access: Bus Width

The 80386 microprocessor supports two types of accesses: Memory, and Input/Output. Each type of access can be 32-, 24-, 16- or 8-bit wide. The memory and I/O devices are 32, 16 or 8 bit wide. The AMI-386 allows any type of access to a device of any width. If necessary, the hardware will split a 80386 bus cycle into a

number of (upto 32 / 8 = 4) cycles to allow access to a 16- or 8-bit device. All the on-board devices in the memory space is organized 32-bit wide. These include the on-board DRAM, the high-speed Cache memory and the EPROM containing the BIOS. All the on-board I/O devices are 8-bit wide, with the exception of the 80387 math coprocessor which is a 32-bit device.

The AMI-386XT can support 16- and 8-bit memory and I/O devices on the I/O slots.

The memory space from address 0C0000 thru 0C7FFF is reserved for I/O slot ROM. Most often, only the EGA BIOS (0C0000-0C3FFF), which is accessed through a 8-bit bus, is located in this area. The slow execution of this device driver makes the video I/O sluggish. The AMI-386 provides the option of mapping this space into the 32 bit system board EPROM. The board is shipped with the AMI EGA compatible BIOS in the system board EPROM, which maps into the required memory space if SWI is ON. Refer to Section 1.3 for SWI setting. This improves the video I/O speed, since the EGA BIOS can now be accessed through a 32-bit bus. When SWI is ON, there should not be any I/O slot 16-bit memory in the address space 0C0000 thru 0C7FFF. Also, any I/O slot 8-bit memory in that space will be automatically disabled.

#### Cache and DRAM access

In 80386, a zero wait-state bus cycle requires two clock cycles. The required number of clock cycles increases by one with every wait-state introduced in the access. Most processor accesses are memory read operations. To speed up the memory reads, the AMI-386 incorporates 64KB of 32-bit wide directly mapped cache, realized with high-speed Static RAM. The cache has byte granularity and a page size of 4 bytes and is implemented with a write-thru algorithm. At 16MHz, with the cache enabled, 81% of data will be available in the cache for memory read operations (this is a statistical value for normal program execution). This improves system speed about twofold, since the cache access requires no wait states, whereas the main memory access would require at least two.

A point to note is that, even the off-board (I/O slot not 32bit memory slot) memory is cached. Hence most read operations, even from a slow off-board memory, will have no wait states. As a result, the speed and bus width of the expansion memory will hardly affect the system speed. However, since an off-board memory always takes longer to access

than the 32 bit memory on the 32bit slot, it is always a good idea to utilize the 32bit memory to its full capacity before resorting to add-on memory boards. Refer to Section 1.3 for 32bit memory switch settings.

Refer to Section 2.C and 3.7 for information on how to enable and disable the cache.

#### Data Access: Cycle times

The following table gives the number of wait states and the total bus cycle times for different cases of Cache and on-board DRAM access:-

|                             | 6MI            | Hz           | 16MHz          |              |

|-----------------------------|----------------|--------------|----------------|--------------|

| Access Type                 | wait<br>states | time<br>(ns) | wait<br>states | time<br>(ns) |

| Memory Read:<br>Cache hit   | -              | -            | 0              | 125          |

| DRAM Read:<br>Cache disable | 1              | 500          | 2              | 250          |

| DRAM Read:<br>Cache miss    | 1              | 500          | 3              | 312.5        |

| DRAM Write                  | 1              | 500          | 2              | 250          |

The table below lists the number of wait states and processor access times for on-board EPROM, I/O and off-board accesses:-

|                                     | 6N             | ſΗz          | 16M  | Hz<br>/,IORD) | 16MH<br>(MEMR  |              |

|-------------------------------------|----------------|--------------|------|---------------|----------------|--------------|

| Access type                         | wait<br>states | time<br>(ns) | wait | time<br>(ns)  | wait<br>states | time<br>(ns) |

| 16-bit device                       | 1              | 500          | 5    | 437.5         | 6              | 500          |

| 8-bit access<br>to 8-bit<br>device  | 4              | 1000         | 10   | 750           | 11             | 812.5        |

| 16-bit access<br>to 8-bit<br>device | 10             | 2000         | 22   | 1500          | 24             | 1625         |

Refresh Controller and DMA Timing

The refresh controller operates at 6 or 8 MHz for processor clock of 6 or 16MHz respectively. Each refresh cycle requires 5 clock cycles to refresh all the DRAM in the sysytem. 256 refresh cycles are required every 4 ms.

The DMA controller operates at 3 or 4 MHz for CPU clock of 6 or 16 MHz respectively. All DMA transfer bus cycles are 5 clock cycles long, which results in a cycle time of 1660 or 1250 ns.

1.XT is a registered trademark of IBM Corp.

# SECTION - 4

# **Technical Specifications**

# 4.1 32bit DRAM memory map

| SW1 SW2                                  | SW3                      | MEMORY<br>BELOW 1MB                          | MEMORY<br>ABOVE 1MB                           |